De la contrainte à la performance :

concevoir des bus DDR5 sans marge d’erreur

🖋️ Par Adrian Piticco

Ingénieur d'application EDA chez Var Industries S.A.S.

Une désynchronisation invisible, un projet en péril

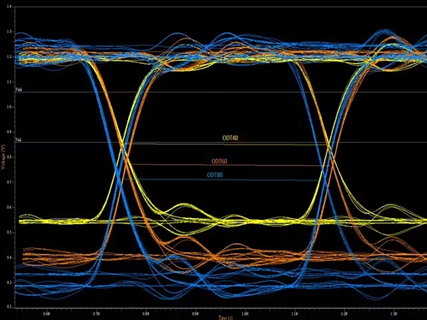

Le café refroidit depuis longtemps. Claire, ingénieure hardware, fixe son écran avec une inquiétude grandissante : un timing report vient de tomber. Le bus DDR5 refuse obstinément de passer en simulation. Les longueurs sont correctes, les paires différentielles bien appariées… mais un décalage de seulement 20 ps entre certaines lignes DQ suffit à fermer l'œil et compromettre la stabilité du système.

À ces vitesses, ce qui était hier un détail devient aujourd'hui une faille critique. Une approximation minuscule, imperceptible dans un routage classique, peut condamner un projet entier. Et avec la DDR5 et les interfaces à plusieurs gigabits par seconde, la marge d'erreur tend vers zéro.

La pression est immense : livrer plus vite, avec moins d'itérations, tout en garantissant une fiabilité irréprochable. Les équipes hardware savent que la moindre hésitation peut coûter des semaines de retard et des milliers d'euros en prototypes supplémentaires.

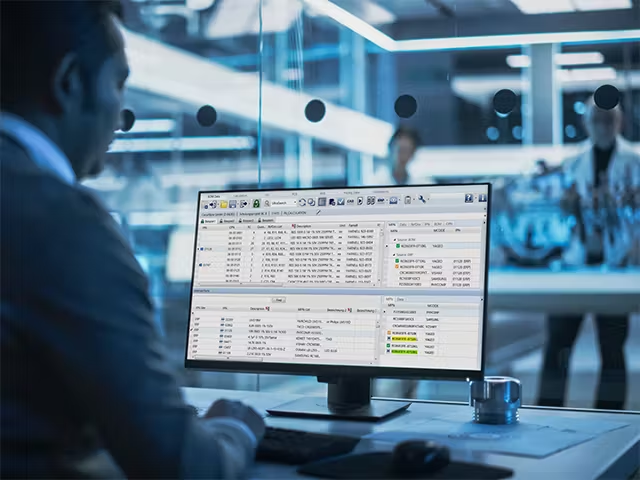

C'est précisément là qu'intervient Xpedition de Siemens EDA, avec deux modules complémentaires conçus pour reprendre le contrôle : Constraint Manager et Sketch Routing.

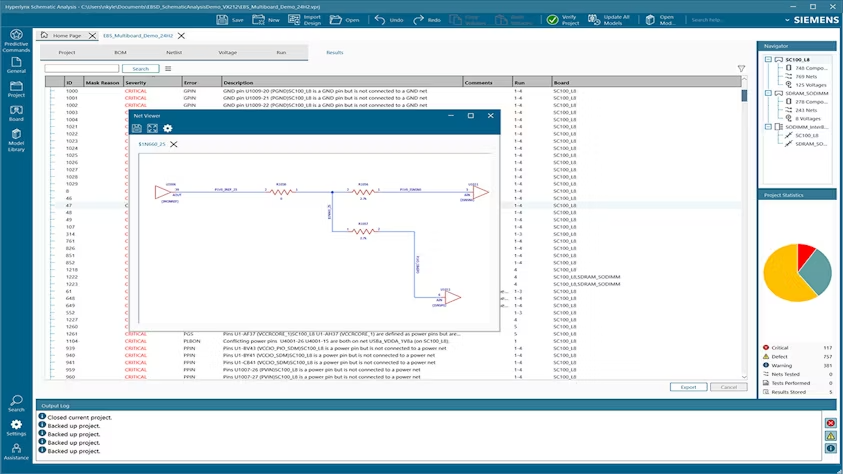

Constraint Manager : transformer les règles en garanties

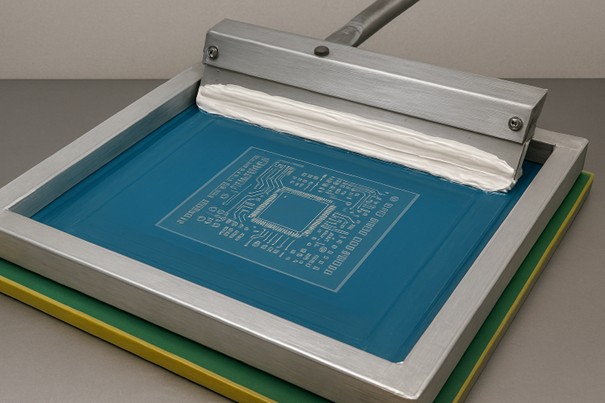

Définir les contraintes DDR5 est une étape incontournable : égalisation des longueurs, alignement des bus, respect des impédances différentielles… Mais poser les règles ne suffit pas : il faut qu'elles vivent dans l'outil, qu'elles guident chaque tracé et qu'elles s'imposent à toutes les étapes du design.

Avec Constraint Manager, les contraintes ne restent pas de simples notes dans un cahier des charges. Elles deviennent des garde-fous intelligents, directement intégrés au PCB.

✅ Vérification proactive des longueurs et du skew.

✅ Gestion hiérarchisée des contraintes (par net, par groupe, par bus).

✅ Validation en temps réel, sans attendre la simulation finale.

✅ Suivi clair et visuel de la conformité du routage.

Résultat : chaque net critique du bus mémoire est surveillé, chaque déviation signalée instantanément, et l'ingénieur avance avec la certitude que son design reste conforme aux tolérances DDR5.

Mais l'impact va plus loin : cette gestion centralisée favorise la collaboration entre concepteurs PCB, ingénieurs signal integrity et responsables système.

Les contraintes deviennent un langage commun, partagé et tracé de bout en bout, ce qui réduit les malentendus et fluidifie la communication au sein de l'équipe.

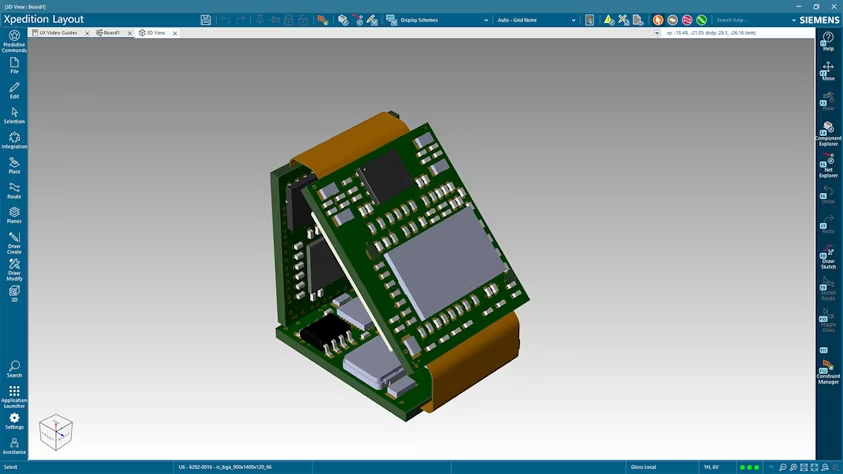

Sketch Routing : accélérer sans sacrifier la qualité

Réaliser un routage DDR5 à la main, c'est un marathon technique. Multiplier les serpentins pour équilibrer les longueurs, aligner manuellement les paires différentielles, répéter les mêmes ajustements fastidieux sur des dizaines de signaux… un travail chronophage, source d'erreurs et de lassitude.

Avec Sketch Routing, la logique change radicalement :

- L'ingénieur esquisse simplement un trajet.

- L'outil génère automatiquement un routage optimal, compact et propre.

- Les égalisations de longueurs sont intégrées de manière intelligente.

- Les contraintes définies dans Constraint Manager sont respectées à la lettre.

En d'autres termes : moins de répétition, plus de productivité et surtout un design DDR5 terminé en une fraction du temps, sans compromis sur la qualité.

Ce gain de vitesse n'est pas un luxe : c'est un levier stratégique. Sur des marchés où les cycles produits se raccourcissent, où chaque trimestre de retard peut représenter une perte de parts de marché, la capacité à livrer un design fiable dès le premier prototype devient un avantage concurrentiel déterminant.

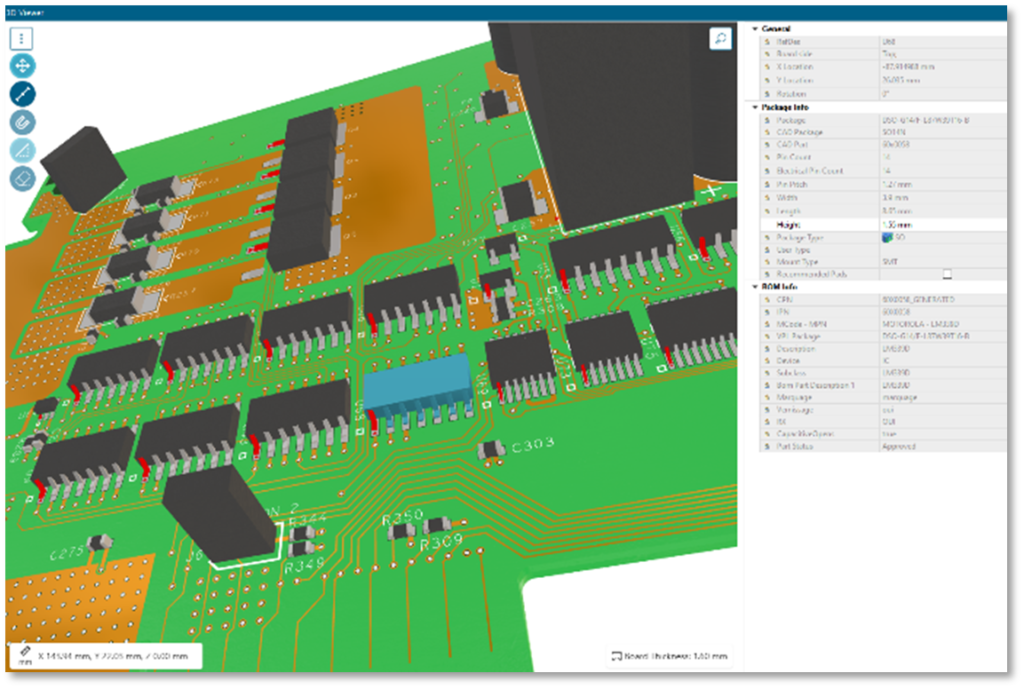

L'intégrité du signal, un impératif absolu

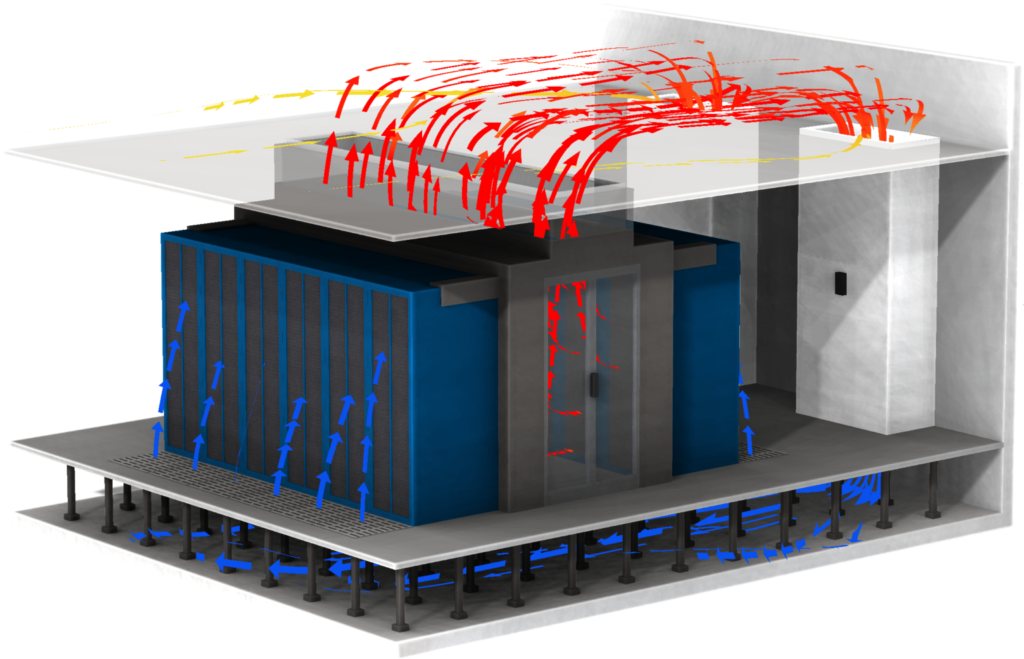

Concevoir en DDR5, ce n'est pas seulement équilibrer des longueurs. C'est aussi anticiper l'ensemble des phénomènes liés aux hautes vitesses : diaphonie, réflexions, pertes en ligne, transitions trop abruptes.

Sans une gestion fine des contraintes et un routage maîtrisé, les simulations d'intégrité de signal se transforment en cauchemar. Chaque itération corrige un problème mais en crée un autre, et la validation s'éloigne à mesure que les semaines passent.

Avec Constraint Manager et Sketch Routing, les simulations ne sont plus un révélateur de catastrophes tardives, mais une confirmation que le design est déjà solide. Cette inversion du paradigme permet de passer d'une logique réactive à une logique proactive, où la conception intègre en amont la discipline du signal integrity.

Des projets plus rapides, moins d'itérations

Chaque erreur non détectée dans un bus DDR5 peut imposer une refonte complète du PCB, avec à la clé des prototypes supplémentaires, des délais rallongés et des budgets qui explosent.

🛠 Exemple concret : Une équipe développant une carte serveur basée sur DDR5 peinait à stabiliser son design mémoire. Chaque itération révélait de nouveaux écarts de timing, entraînant des semaines de retard et des coûts non prévus. Après avoir intégré Constraint Manager et Sketch Routing, le premier routage a directement passé les vérifications de timing et d'intégrité de signal. Résultat : un seul prototype validé, un gain de plusieurs semaines et une réduction significative du budget développement.

C'est tout l'enjeu : transformer un parcours semé d'embûches en un processus fluide, maîtrisé et prévisible.

Conclusion : concevoir à la vitesse de demain

Avec DDR5 et les technologies de nouvelle génération, concevoir un PCB n'est plus une simple affaire de placement et de routage. C'est une discipline de précision, où chaque picoseconde compte et où chaque décision influence la fiabilité du produit final.

Avec Xpedition, ce défi devient un avantage compétitif :

✅ Des règles appliquées automatiquement grâce à Constraint Manager.

✅ Un routage accéléré et maîtrisé grâce à Sketch Routing.

✅ Moins d'itérations, plus de sérénité, et des designs prêts pour la cadence des technologies de demain.

Et l'histoire ne s'arrête pas là. Ce qui est vrai pour DDR5 le sera bientôt pour DDR6, PCIe Gen6 ou les interconnexions multi-gigahertz des futurs data centers. Plus la vitesse monte, plus la marge d'erreur diminue. Les ingénieurs ont besoin d'outils capables d'anticiper cette complexité croissante, et Xpedition s'inscrit déjà dans cette trajectoire.

Parce qu'à ces vitesses, l'ingénieur n'a pas le droit au doute. Il lui faut des solutions qui garantissent la fiabilité, tout en laissant la voie libre à l'innovation. Avec Xpedition, la conception électronique n'avance plus au rythme d'hier, mais à la vitesse de demain.

Vous êtes confronté(e) à ces enjeux ? Contactez-nous pour découvrir comment nous pouvons vous accompagner concrètement.

Notre expert commercial :

Frédéric Benamor – Chief Sales Officer

📧 f.benamor@cadlog.com | ☎️ +33 6 30 94 63 15

ARTICLES SIMILAIRES :

Vous voulez rester à jour sur le monde de l'électronique?

Inscrivez-vous à la newsletter de Cadlog!